Edge Computing Gateway PCB Design: A Systematic Approach to Balancing Multiple Network Interfaces, Local Computing Power, and Low Power Consumption

As a key node in the Internet of Things (IoT) and the Industrial Internet of Things (IIoT), the PCB design of edge computing gateways must simultaneously meet three rigid requirements under constraints such as limited physical space, stringent heat dissipation conditions, and diverse power supply methods (e.g., batteries, PoE, wide voltage adaptation): high-bandwidth multi-protocol access, real-time local AI/data processing, and long-term stable low-power operation. This is not a matter of parameter trade-offs, but a systematic engineering project involving material selection, layer stack-up planning, signal integrity, thermal management, and power architecture. The following provides a professional analysis from four dimensions.

Network Interface Integration: A Design Paradigm for High Speed, Isolation, and EMI Coexistence

Modern edge gateways generally need to support heterogeneous network protocols such as 5G NR, Wi-Fi 6/7, Zigbee, Thread, TSN Ethernet (2.5G/5G), CAN FD, and RS-485. The core challenge in its PCB design lies in the vulnerability of high-frequency radio frequency (RF) paths to digital noise interference, and the coexistence of multiple protocols exacerbating crosstalk risks.

Physical Layer Isolation and Stack-up Optimization: A 10-layer or higher HDI (High-Density Interconnect) structure is employed, clearly defining the RF zone, high-speed digital zone, analog sensing zone, and power zone. For example, in the RK3588 platform gateway design, the 5G module is isolated through an independent shielded cavity, and its antenna feed uses a 50Ω microstrip line with full ground coverage to avoid crossing the digital plane; the Ethernet PHY chip is placed in an independent area away from the CPU main power supply and configured with a dedicated ferrite core and TVS array.

Impedance Control and Termination Matching: All high-speed differential pairs (PCIe Gen3, USB 3.2, MIPI CSI) undergo ±5% impedance tolerance control; Gigabit Ethernet interfaces must implement AC coupling capacitors + terminating resistor matching to prevent reflections from increasing the bit error rate.

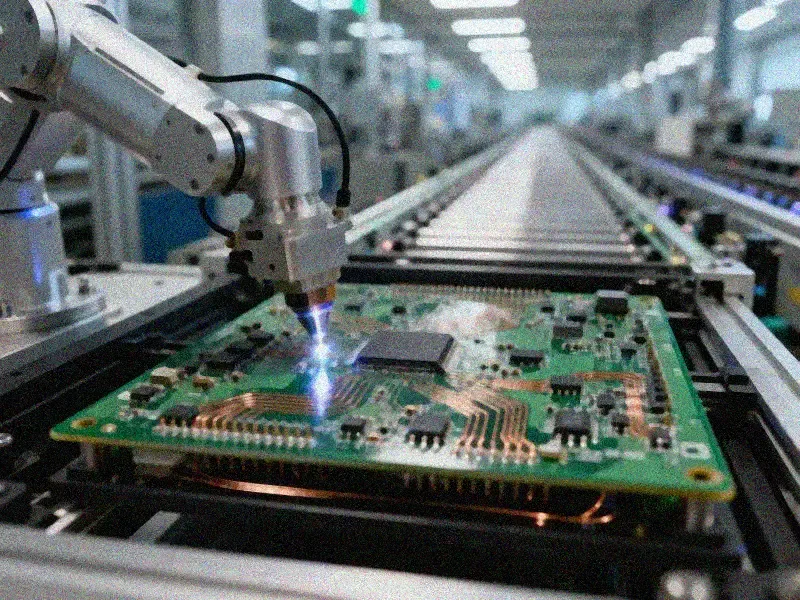

EMC/EMI Enhancement Process: The entire board undergoes immersion gold (ENIG) surface treatment to improve high-frequency soldering reliability; grounding vias are arranged around key RF traces with a spacing ≤λ/10 (≤3cm at 1GHz); copper plating is added to the PCB edges and connected to the chassis ground, creating a Faraday cage effect.

Practical Verification: A 5G edge controller project achieved an EMC radiated emission (RE) margin of 8dB through the above design, far exceeding the CISPR 32 Class B limit.

Local Computing Capability: Heat Dissipation, Power Supply, and Signal Integrity Guarantee for High-Performance SoCs

Edge gateways often utilize high-performance SoCs such as the RK3588, NVIDIA Jetson Orin, or Intel Atom x6000E, with typical power consumption ranging from 12–25W. These chips place three stringent requirements on the PCB: transient high-current power supply stability, precise junction temperature control, and high-speed bus signal fidelity.

Power Supply Architecture Design:

- The main power supply adopts a hybrid "multi-phase DC-DC + local LDO" scheme: the SoC core voltage (VDD_CPU) is provided by a 4-phase VRM, each phase carrying ≥5A current. The corresponding power plane on the PCB uses 2oz thick copper (≥70μm), and the width of critical power traces is ≥3mm;

- To reduce PDN (Power Distribution Network) impedance, a large area of copper pour is placed below the SoC pads, with dense vias connecting to the inner power plane. The target impedance is <10mΩ@10MHz;

- All power input ports are equipped with π-type filters (common-mode inductor + X/Y capacitor) to suppress conducted interference entering the system.

Engineering Implementation of Thermal Management:

- The preferred substrate is FR-4 high TG (Tg≥170℃) or an aluminum substrate (thermal conductivity>1.5 W/m·K), ensuring mechanical strength is maintained even at an ambient temperature of 85℃;

- A thermal via array is designed on the PCB area directly below the SoC, with a hole diameter of 0.3mm and a spacing of 0.8mm, filled with thermal paste before connecting to the heatsink base;

- The entire system employs a three-stage thermal chain: "PCB copper layer thermal conductivity + metal casing heatsink + intelligent fan speed control." In actual testing, the SoC junction temperature remained stable below 82℃ under full load.

High-Speed Signal Integrity (SI) Control:

- Strictly equal-length (±5mil) traces for DDR4/LPDDR4x memory, with ground plane protection and continuous, unsplit reference planes;

- Backdrilling process is implemented for PCIe Gen3 channels to eliminate stub effects, achieving insertion loss <-25dB@8GHz;

- All high-speed signal interlayer dielectric thickness ≤3mil, dielectric constant Dk controlled at 3.6±0.1 (Rogers RO4350B mixed-voltage solution).

Low-Power Design: Full-Stack Optimization from Component Selection to Dynamic Power Management

Edge gateways are often deployed in scenarios without mains power (such as agricultural sensor nodes and field monitoring stations), requiring standby power consumption to be controlled in the 50–200mW range, which places high demands on PCB design.

Ultra-Low Quiescent Current Device Applications:

- Use LDOs with a quiescent current (IQ) < 1μA (such as the TPS7A05 series) to power the RTC and sensors;

- When the MCU is in sleep mode, all unused peripheral power domains are shut down. Power supply switches for each module are controlled via the PMIC's GPIO, cutting off leakage current paths.

PCB-Level Power Consumption Suppression Technology:

- Use OSP (Organic Solder Protector) surface treatment instead of immersion gold to reduce surface leakage risk (especially in high humidity environments);

- Power plane segmentation design: Independent copper foil areas are set up for different voltage domains (3.3V/1.8V/1.1V) to avoid cross-domain coupling leakage;

- 0Ω resistors are connected in series on critical signal lines to reserve debugging points and avoid potential short-circuit risks caused by direct connections.

Dynamic Power Management (DPM) Hardware Support:

- Integrated high-precision current sensing circuit (shunt resistor + op-amp) on the PCB, with a sampling accuracy of ±0.5%, providing real-time feedback to the MCU;

- Designed independent "Low-Power Monitoring Unit" that reads voltage/temperature/current using an ADC to trigger deep sleep or wake-up interrupts.

Note: Low power consumption does not equate to sacrificing performance. A case study of a smart environment controller shows that through DPM strategies and PCB-level optimization, the average power consumption of the entire system was reduced by 42%, while the response latency was shortened by 18% (due to reduced invalid polling).

System-Level Collaboration: Rigid-Flex, Conformal Processing, and IPM Manufacturing Closed Loop

Single technology optimization cannot resolve systemic contradictions; advanced manufacturing processes are needed to achieve multi-objective unification:

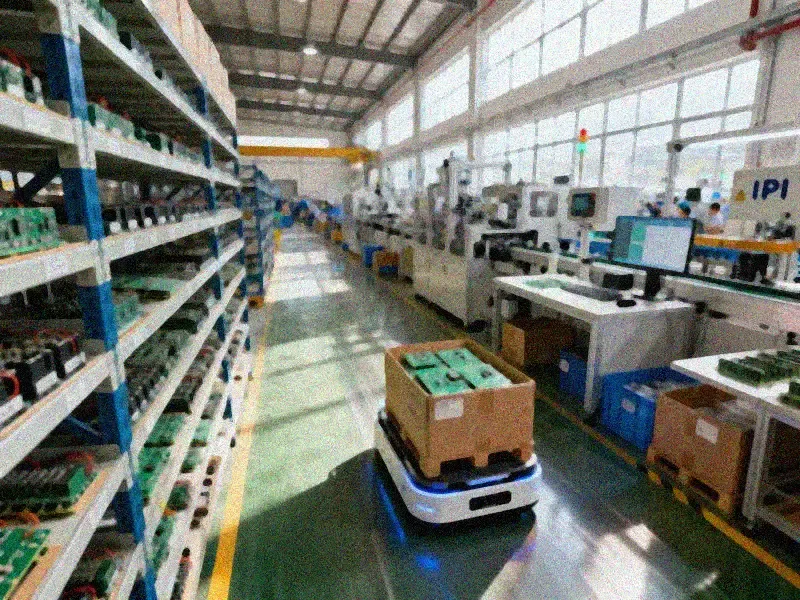

Rigid-Flex Application: Integrating the main control board (rigid) with the antenna/sensor daughterboard (flexible) into a single design reduces contact resistance and EMI radiation sources introduced by connectors, while saving over 30% of space;

Triple Conformal Processing (IPM):

- Chemical Protection: The entire board is coated with polyurethane conformal paint conforming to IPC-CC-830B standards (50–70μm thickness), with salt spray resistance >1000 hours;

- Structural Protection: Strong and weak current areas employ SCH (Separation & Creepage Height) isolation design, with a minimum electrical clearance ≥8mm;

- Environmental Protection: Silicone sealing rings are added to the interface area, and conductive silver paste is applied to the PCB edges to achieve both electromagnetic shielding and moisture protection.

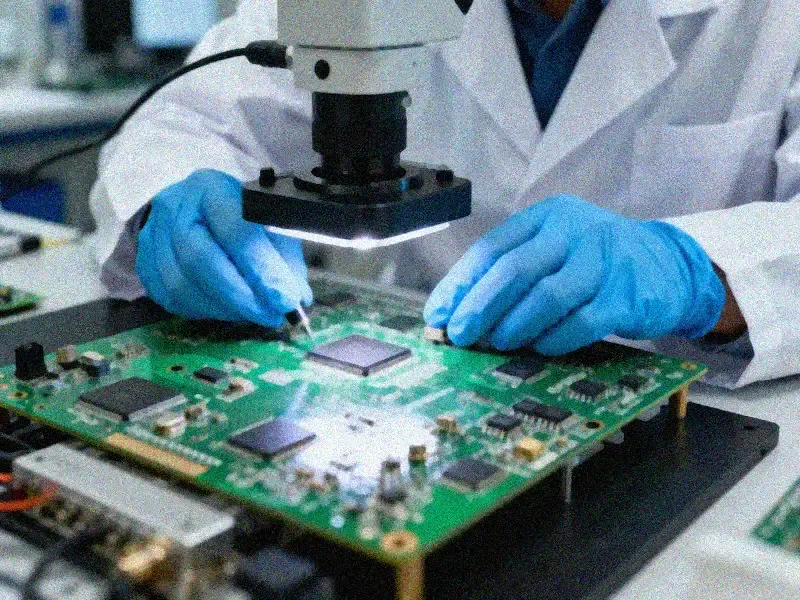

IPDM (Integrated Product Design and Manufacturing) Closed Loop: From BOM selection (domestic alternative material library covering 3.27 million certified components), DFM manufacturability analysis (2368 rules for automatic verification), to full coverage of flying probe testing, ensuring a first-time design success rate of >95% and reducing mass production cycle to 60% of the industry average.

A Balanced Approach for the Future

The essence of edge computing gateway PCB design is seeking the optimal solution for the system under the constraints of physical laws. It requires engineers to move beyond "single-point optimization" thinking and deeply integrate materials science (high thermal conductivity substrates), electromagnetic theory (SI/PI simulation), thermodynamics (heat dissipation modeling), and manufacturing engineering (rigid-flexible processes) within the framework of IPDM methodology. Only in this way can we deliver the cornerstone of edge intelligent hardware that combines high performance, high reliability, and long battery life in the 5G+AIoT era.